3D-Chips auf dem Vormarsch:

Herausforderungen bei Testverfahren

Gerade jetzt am Ende des wirtschaftlichen Abschwungs lässt sich eine rasche Umstellung von 2D- auf 3D-Gehäuse feststellen. Bewahrheiten sich die Aussagen eines Analysten von Gartner Inc., dann stehen der Branche in der Aufschwungphase einige große Herausforderungen bei den Testmethoden bevor.

Zwar sind 3D-Chipfertigungs-Techniken schon seit vielen Jahren bekannt. Auch konnten bei den Fertigungstechnologien für 3D-Chips bereits große Fortschritte erzielt werden. Ein Hauptproblem bei Tests von 3D-Chips ist jedoch noch der Zugriff, genauer gesagt der fehlende Zugriff. Das Aufeinanderstapeln mehrerer Halbleiter-Dies kann dazu führen, dass auf einen oder mehrere Dies von extern nicht zugegriffen werden kann, sofern eine Testtechnologie genutzt wird, die mit einer physischen Sonde arbeitet. Die Halbleiterhersteller haben dies erkannt und betten jetzt verschiedene Arten von Test- und Messinstrumenten in ihre Cores ein. Dadurch können die Chips die Instrumente intern ansteuern. Diese eingebetteten Instrumente können Bedingungen auf dem Chip überwachen, Daten erfassen und die Ergebnisse an eine externe Testplattform wie ScanWorks übermitteln.

Offene Umgebung

Mehrere neue IEEE-Standards sind bereits in Arbeit, die eine offene Umgebung schaffen werden, wie sie für die Entwicklung von Drittanbietertools erforderlich ist. Bei diesen neuen Normen handelt es sich um IEEE 1149.7, eine Erweiterung und Fortführung des ursprünglichen IEEE 1149.1 Boundary-Scan-Standards und um IEEE P1687, den sogenannten internen JTAG-Standard (IJTAG). Adam Ley, Chief Scan von Asset, hat in der 1149.7 Arbeitsgruppe mitgewirkt und einen Großteil der Testinhalte zusammengetragen, die in dem Standard enthalten sind. Eine weitere Führungskraft von Asset, Al Crouch, Chief Technologist Core Instrumentation, ist der Co-Chairman der IEEE P1687 Arbeitsgruppe. Diese beiden Standards sowie andere Normen, die bereits von der Industrie eingeführt wurden, markieren den Anfang der Ära eines Ökosystems von Standards, die eine offene Umgebung schaffen, in der Drittanbieter wie Asset die Tools entwickeln können, die für das Testen von 3D-Chips erforderlich sind. Mehrere Standards spielen innerhalb dieses Ökosystems zusammen.

Ansteuerung über eine Testplattform

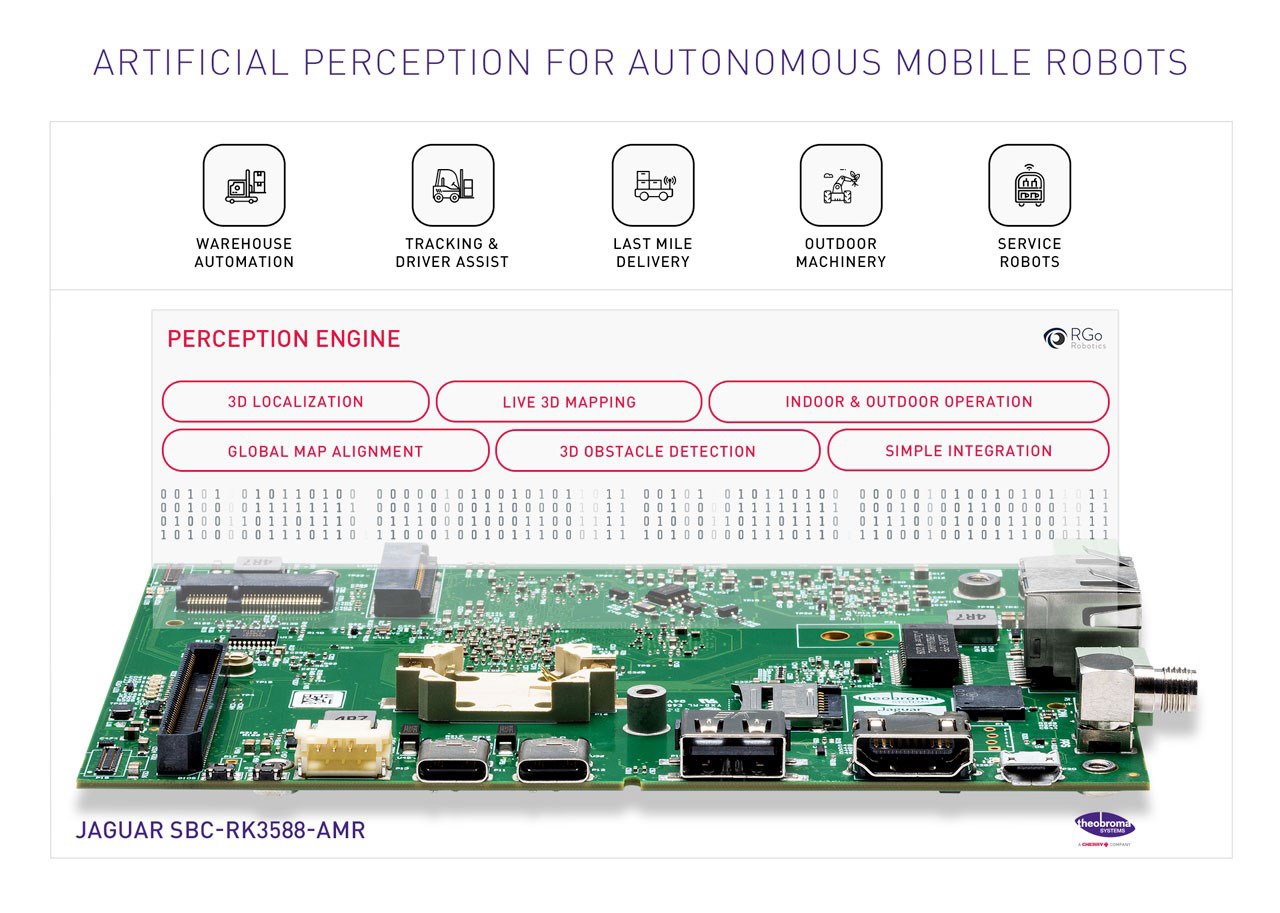

Die hier abgedruckte Abbildung ist eine 2D-Darstellung eines 3D-Konzepts. Um sich die Abbildung in 3D vorzustellen zu können, müssen mehrere dieser 2D-Darstellungen im Geiste übereinander gelegt werden. Der Rand jedes Die im Stack wäre mit Boundary-Scan-Zellen besetzt. In diesem Fall wird eine 1149.7-Zweidrahtschnittstelle auf der Komponente genutzt, um die Kosten für den Chip-Zugriff zu senken. Die interne 1149.7 Architektur ist eine Sterntopologie. Es wird zwar in dieser Darstellung nicht gezeigt, aber die Sternarchitektur lässt sich mit TSVs (Through-Silicon Vias) zu einem Die unter dem Die im Blockdiagramm ausdehnen. 1149.1 TAPs (Test Access Ports) bilden den vorderen Abschluss des IEEE 1500-Wrapper jedes Chip-Cores, sodass jeder dieser Cores so behandelt werden kann, als sei es ein Chip mit einem JTAG-Port. Jeder Core enthält auch ein oder mehrere eingebettete Instrumente für Test- und Messzwecke, die mit dem IEEE P1687-Standard konform sind. Durch Einhaltung des P1687-Standards erfolgt die Ansteuerung, Automatisierung und Verwaltung all dieser Instrumente über eine einzige Testplattform. Diese kann die von den Instrumenten gelieferten Daten auswerten. Das Blockdiagramm zeigt zudem, dass diese Standards mit proprietärer eingebetteter Instrumentation kompatibel sein können. Die eingebettete BIST-Instrumentationstechnologie (Interconnect Built-In Self Test) von Intel wird an der Peripherie des Dies dargestellt, wo sie für SerDes BIST-Tests

und -Validierung genutzt werden kann.

Autor: Glenn Woppman, President und CEO, Asset InterTech