Systemoptimierung und BoM-Reduktion

Lukrativer entwickeln

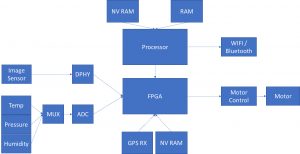

Ein entscheidender Faktor, um laufende Entwicklungskosten zu senken, ist die Implementierung mit engerer Systemintegration. Dazu zählt auch die Integration auf der Komponentenebene. Ein typisches eingebettetes System enthält heute zahlreiche Funktionsträge, wie Prozessoren, digitale Logikschaltungen, Schnittstellern, flüchtige und nichtflüchtige Speicher, Sensoren, außerdem Support-Elemente wie Taktgeber. Ein höherer Integrationsgrad reduziert die Systemkomplexität und damit auch die Kosten für die Leiterplatten und deren Bestückung.

Embedded-Systeme für existierende und neu entstehende Anwendungen durchlaufen derzeit eine Phase rapiden Wachstums. Analysten gehen davon aus, dass der Markt für eingebettete Systeme bis 2021 ein Volumen von 225 Mrd. Dollar erreichen wird. Dieses Wachstum wird getragen von der kontinuierlichen Fortschreibung wichtiger industrieller Megatrends wie IoT, IIoT, Industrie 4.0 und cyberphysikalische Systeme. Hinzu kommt, dass sich Vision-gestützte Systeme vermehrt an der Edge etablieren. Viele dieser Applikationen erfordern dazu den Einsatz von High-Performance Systemen. Bei Applikationen, die eine große Zahl von Standorten und Einrichtungen umfassen, sind die laufenden Entwicklungskosten der Lösung von kritischer Bedeutung. Sie bestimmen deren Wirtschaftlichkeit. Einer der entscheidenden Faktoren zur Reduktion der laufenden Entwicklungskosten ist die Implementierung mit engerer Systemintegration.

Applikationsanforderungen

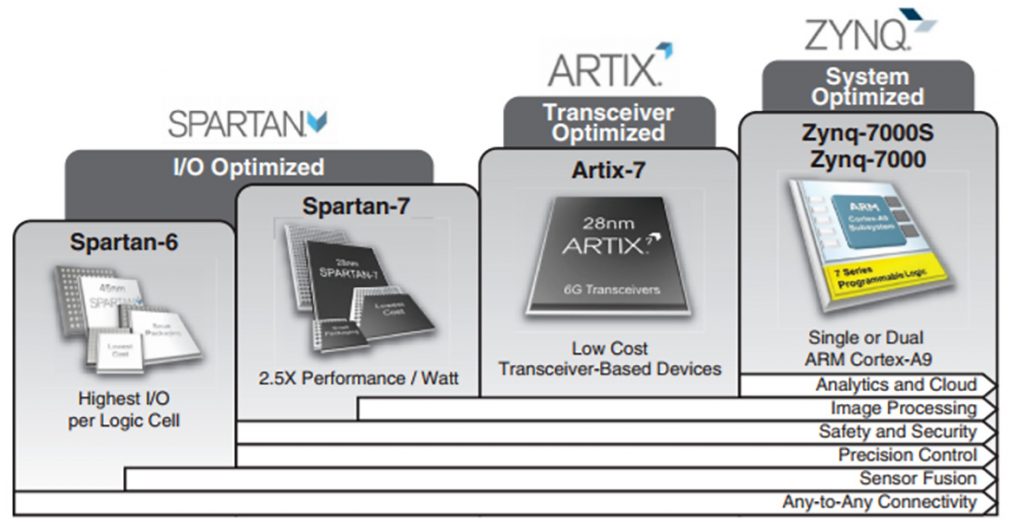

All Programmable Bausteine wie FPGAs (Field Programmable Gate Arrays) und heterogene SoCs (System on Chip) aus dem Xilinx-Portfolio, das die Systemkosten im Blick behält, bieten nicht nur die geforderte Performance. Sie ermöglichen auch die Realisierung der angestrebten engeren Systemintegration. Die Bausteine sind auf unterschiedlichen Applikationsanforderungen zugeschnitten:

• I/O-Optimierung – bereitgestellt von der Spartan-6- und Spartan-7-Familie

• Transceiveroptimierung – bereitgestellt von den Artix-Familie mit Gigabit-Transceivern

• Systemoptimierung – bereitgestellt von den Zynq-7000 SoC Dual-Core Cortex-A9- und den Single-Core Cortex-A9-Familien.

Das Xilinx-Portfolio deckt zahlreiche unterschiedliche Applikationen ab: vom Cloud Computing und der Bildbearbeitung bis zur Sensor-Fusion, präzisen Steuerungen sowie den Safety- und Securitybereich (Bild 1). Mit dem Einsatz dieser Baustein-Suite lassen sich wesentlich höher integrierte Systeme realisieren, insbesondere in Bezug auf:

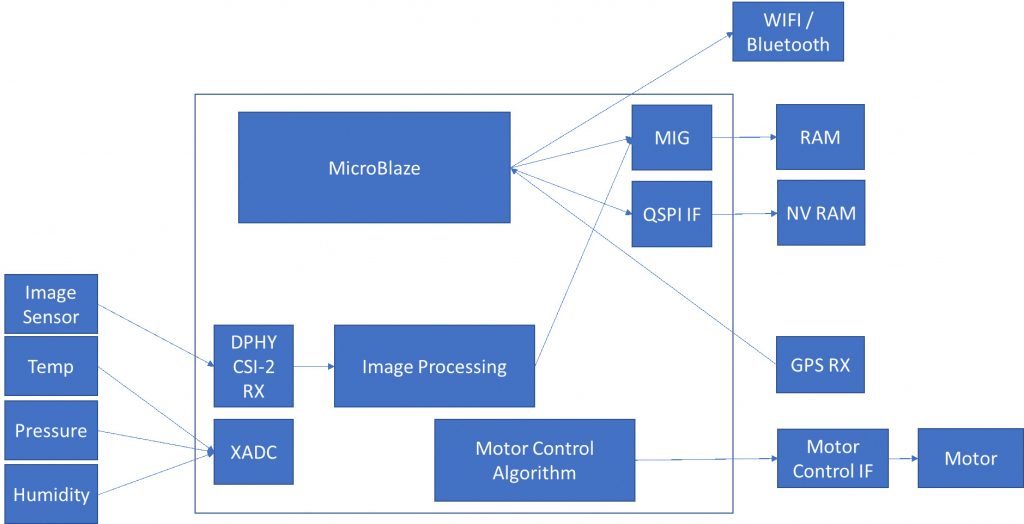

• Prozessorintegration – durch die Kombination von Prozessor und digitaler Logik in demselben Baustein. Dies lässt sich erreichen durch den Einsatz des 32Bit MicroBlaze Softcore-Prozessors oder der Zynq-7000 Cortex-A9-Kerne.

• Mixed-Signal Integration – durch die Nutzung der analogen Fähigkeiten der Bausteine der Serie 7. Der Analog/Mixed-Signal Modul XADC umfasst duale ADCs mit 1 MSample/s, die das interne Multiplexen von 17 differenziellen Eingängen ermöglichen. Für DAC-Funktionen kann die Pulsbreitenmodulation eingesetzt werden. Bei höheren Samplingraten lassen sich auch Delta-Sigma-Verfahren implementieren, unter Nutzung der differenziellen Fähigkeiten der I/O-Zellen.

• Schnittstellenvereinfachung – Mit der programmierbaren Logik lässt sich, wegen des breiten Bereichs der direkt von den I/O-Strukturen unterstützten Standards, ein universelles Any-to-Any Interface implementieren. In Verbindung mit der Implementierung von Protokollfunktionen in der programmierbaren Logik erlaubt dies die einfache Konfigurierung von Standard-, Legacy- und maßgeschneiderten Schnittstellen. Diese Flexibilität ermöglicht auch eine Verringerung der erforderlichen diskreten PHY-Bausteine, wie HDMI oder MIPI DPHY.

• Vereinfachung der Speicherarchitektur – Mit einem einheitlichen Ansatz wird es möglich, die Anwendungssoftware und den FPGA-Bitstream innerhalb desselben nichtflüchtigen Speichers abzulegen. Flüchtige Speicher wie DDR lassen sich vom Prozessor und der FPGA-Applikation gemeinsam nutzen.

• Vereinfachte Taktgeberarchitektur – Die Integration in nur einem Baustein umgeht die Notwendigkeit getrennter Oszillatoren für die digitale Logik und die Prozessoren. Dabei können Clock Management Tiles, PLLs (Phase-Locked Loop) und MMCMs (Mixed-Mode Clock Manager) eingesetzt werden, um zusätzliche Systemtakte zu erzeugen und den agilen Abgleich von Frequenz und Phase zu ermöglichen.

Die Entwicklung derartig integrierter Applikationen kann auch die breite Vielfalt von IP-Kernen nutzen, die in der Vivado-Bibliothek zur Verfügung stehen. Außerdem kann man in Applikationen mit algorithmischer und Bild/Signalverarbeitung auch die High-Level Synthese nutzen, um die Funktionalität über High-Level Sprachen wie C oder C++ zu definieren. Das verkürzt die Gesamtentwicklungszeit.